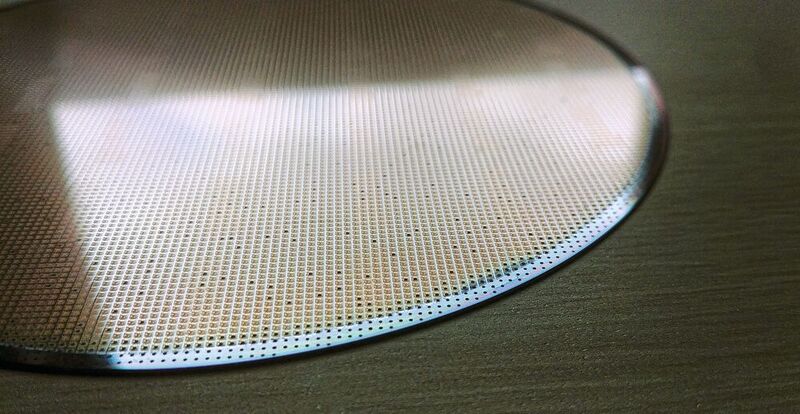

Technik kurz erklärt Die Entwicklung des Silizium Wafers

In unserer Serie „Technik kurz erklärt“ stellen wir jede Woche ein Meisterwerk der Konstruktion vor. Heute: Der Silizium Wafer.

Anbieter zum Thema

Wafer werden aus hochreinem, nahezu fehlerfreiem monokristallinen Silizium mit einer Reinheit von 99,999999999 % oder höher gebildet.

Das gebräuchlichste Verfahren zur Herstellung kristalliner Wafer ist das vom polnischen Chemiker Jan Czochralski erfundene Czochralski-Wachstum. Bei diesem Verfahren wird durch Ziehen eines Impfkristalls aus einer Schmelze ein zylindrischer Barren aus hochreinem monokristallinem Halbleiter, wie Silizium oder Germanium, gebildet.

Wafer Herstellung

Durch langsames kontrolliertes Heben unter Rotation erhält man die charakteristisch geformten runden Säulen (Ingots), die im Fall von Silizium heute üblicherweise einen Durchmesser von ca. 200 oder 300 mm und 2 m Höhe haben.

Portionieren, sägen, polieren

Der sogenannte Ingot wird dann mit einer Wafersäge (einer Art Drahtsäge) etwa 1 mm dick geschnitten und zu Wafern poliert. Wafer für die Photovoltaik haben typischerweise 100 – 200 mm Diagonale und eine Dicke von 100-500 μm. Die Elektronik verwendet Wafergrößen von 100 mm – 450 mm Durchmesser, wobei die 450 mm Wafer durch ihr Gewicht ein Handling-Problem haben. Intel will das aber, laut eigener Aussage bis 2020 gelöst haben.

Alternative Materialien und Preis

Meist wird für Silizium als Material für die Wafer genutzt, es gibt aber auch Wafer aus Gallium-Arsenid, Gallium-Nitrid oder Silizium-Carbid. Vor allem in der LED-Fertigung ist Gallium-Nitrid und Saphir weit verbreitet.

Kosten für bearbeitete Wafer – sogenannte strukturierte Wafer – steigen mit der Anzahl der Prozessschritte erheblich an. Fertige geätzte Computerchips auf einem durchschnittlichen 200-mm-Wafer mit einer Strukturgröße von 90 nm liegen bei ca. 850 Euro je Wafer.

(ID:46267075)

:quality(80)/p7i.vogel.de/wcms/f0/e0/f0e03513954790ec1e2fc12d03a49644/01-poeppelmann-neue-geschaeftsfuehrung-cmyk-2047x1151v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/ad/3b/ad3be25f9d6d69a199ae1126efef4fac/clipboard01-1797x1011v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/02/55/0255a6e34769688d7fb83027a7ac08cf/geralt-business-3468267-6000x3373v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/65/7a/657a5b90c95bf5514eb919d77f44d0d3/260508-pi-ki-wird-chef-arbeitswelt-web-4000x2248v1.png)

:quality(80)/p7i.vogel.de/wcms/b6/05/b605dec1bdfef04619ad964c1a219e9d/hauptbild-studie-2026-viel-ki-nichts-dahinter-2560x1439v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/28/eb/28eb296e910f7bc775e42825546589ad/german-innovation-award-2026-ceremony-16-1500x843v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/6a/5b/6a5bd13e21fa78fac27c6c23ab2c4684/0131354784v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/9c/ae/9caea0d338b6a2ce6af4b1ed25512a29/adobestock-38685209--c2-a9-20benbro-20-e2-80-93-20stock-adobe-com-2814x1584v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/35/31/353100a682a9cb41928f211747dae5e3/rainland-hochaufloesend-2135x1201v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/70/2d/702d0de3a5b4cba0a0b512077cc58c75/bild1-3356x1888v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/d6/81/d681c5707833b407f76c7c370165b873/apic-flt-vpt-mld-2-msi-md-fb-muting-parallel-4-15cm-300dpi-1772x997v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/d6/c1/d6c1a928ee83e288964830a196e1fd0b/item-20fa-20maschinenrichtlinie-20bild1-3000x1687v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/41/a7/41a79c3bb48e11f4c2ae8b33365bcd2f/engin-akyurt-euro-6771167-8192x4608v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/36/93/36938d694f48ccd4d1f5f9e401fee836/adobestock-704571920--c2-a9-20gumpapa-20-e2-80-93-20stock-adobe-com-6000x3373v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/2f/2b/2f2b46d8cd0987790d053a0ecc434833/aumovio-pp-dtco-1-1772x997v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/bf/45/bf4523ff21e3add62ccd8390c5bfea7a/adobestock-726557427--c2-a9-20vladan-20-e2-80-93-20stock-adobe-com-ki-generiert-3580x2016v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/bc/49/bc4957f73a884d8ee1356914659cf2f4/adobestock-325234002--c2-a9-20karyna-20-e2-80-93-20stock-adobe-com-5490x3087v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/7a/22/7a22898e1ee01157399158bd2d7f26c6/0128676654v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/a1/64/a16493ce8f1e75a27e82aba33532b391/lineartechnik-einfach-erklaert-definition-vorteile-anwendungv1.jpeg)

:quality(80)/p7i.vogel.de/wcms/45/8a/458add2ba48d38497829522cac80bbae/reinraum-fuer-pharma-medizintechnik-7-herausforderungen-und-wie-sie-sie-loesenv1.jpeg)

:quality(80)/p7i.vogel.de/wcms/0b/c3/0bc3f807a69dbb07898026e24c11ea06/mini-environments-optikfertigung-neuv1.jpeg)

:fill(fff,0)/p7i.vogel.de/companies/65/c2/65c21eabecee3/hw-logo-blue-rgb.png)

:fill(fff,0)/images.vogel.de/vogelonline/companyimg/107700/107704/65.jpg)

:fill(fff,0)/p7i.vogel.de/companies/64/1b/641b1b39912ca/heraeus-wm-amloy-untereinander-rgb.png)

:quality(80)/p7i.vogel.de/wcms/ca/b5/cab5a723ed4d853ebb41975ea7fb6136/0125723793v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/24/92/249226685e2c54c220829e32eceeae4c/0128031351v2.jpeg)